# EE 330 Lecture 36

## Digital Circuit Design

- Basic Logic Gates

- Properties of Logic Families

- Characterization of CMOS Inverter

## Exam Schedule

Exam 1 Exam 2 Exam 3 Final Friday Sept 24 Friday Oct 22 Friday Nov 19 Tues Dec 14 12:00 p.m.

As a courtesy to fellow classmates, TAs, and the instructor

Wearing of masks during lectures and in the laboratories for this course would be appreciated irrespective of vaccination status

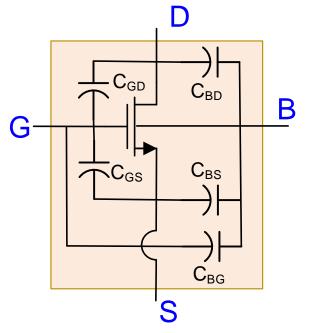

### Review from Last Lecture Parasitic Capacitance Summary

|                 | Cutoff                   | Ohmic                                                                                    | Saturation                                  |

|-----------------|--------------------------|------------------------------------------------------------------------------------------|---------------------------------------------|

| C <sub>GS</sub> | CoxWL <sub>D</sub>       | 0.5C <sub>OX</sub> WL                                                                    | CoxWL <sub>D</sub> +(2/3)C <sub>OX</sub> WL |

|                 | CoxWL <sub>D</sub>       | 0.5C <sub>OX</sub> WL                                                                    | CoxWL <sub>D</sub>                          |

| C <sub>BG</sub> | CoxWL (or less)          | 0                                                                                        | 0                                           |

| C <sub>BS</sub> | $C_{BOT}A_S + C_{SW}P_S$ | C <sub>BOT</sub> A <sub>S</sub> +C <sub>SW</sub> P <sub>S</sub> +0.5WLC <sub>BOTCH</sub> | $C_{BOT}A_{S}+C_{SW}P_{S}+(2/3)WLC_{BOTCH}$ |

| C <sub>BD</sub> | $C_{BOT}A_D + C_{SW}P_D$ | C <sub>BOT</sub> A <sub>D</sub> +C <sub>SW</sub> P <sub>D</sub> +0.5WLC <sub>BOTCH</sub> | $C_{BOT}A_{D}+C_{SW}P_{D}$                  |

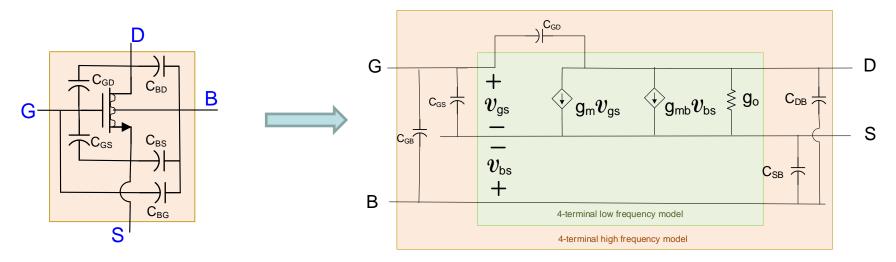

### Review from Last Lecture Parasitic Capacitance Summary

High Frequency Large Signal Model

High Frequency Small Signal Model

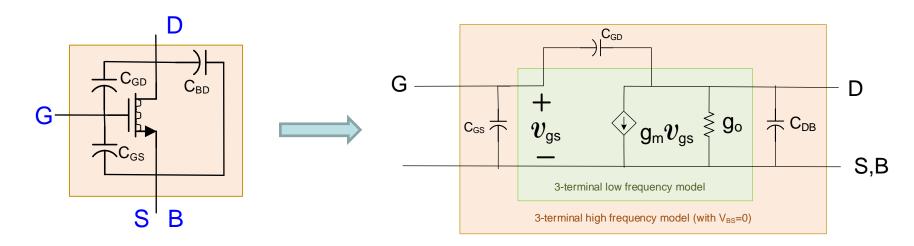

Often  $V_{BS}=0$  and  $C_{BG}=0$ , so simplifies to

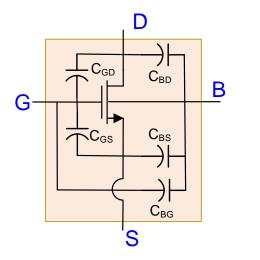

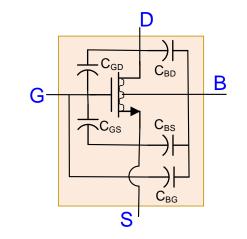

#### **Review from Last Lecture**

# High Frequency Small-Signal Model

#### Often $V_{BS}=0$ and $C_{BG}=0$ , so simplifies to

# High Frequency Small-Signal Model

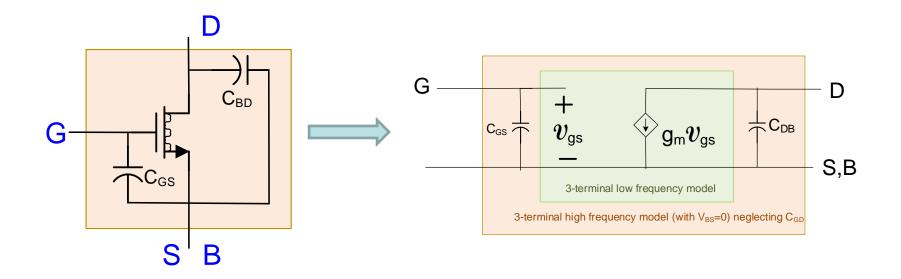

Often  $V_{BS}=0$  and  $C_{BG}=0$  and  $C_{GD}$  and  $g_0$  can be neglected so simplifies farther to

Neglecting  $C_{GD}$  which is high frequency feedback from output to input often simplifies analysis considerably

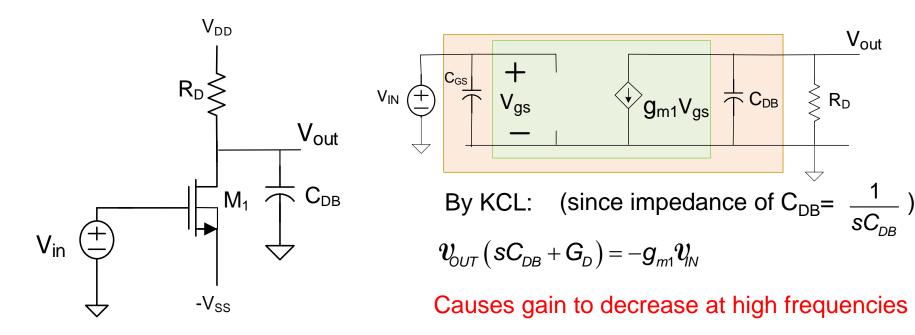

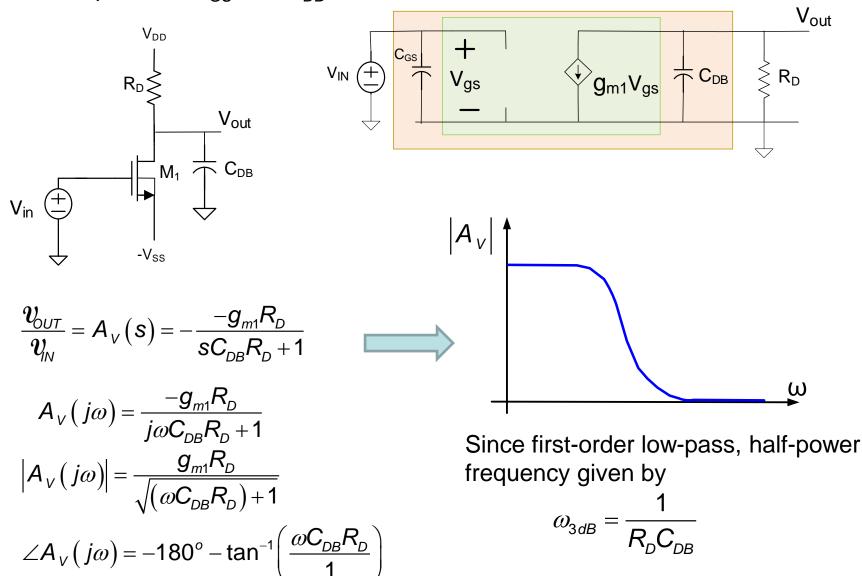

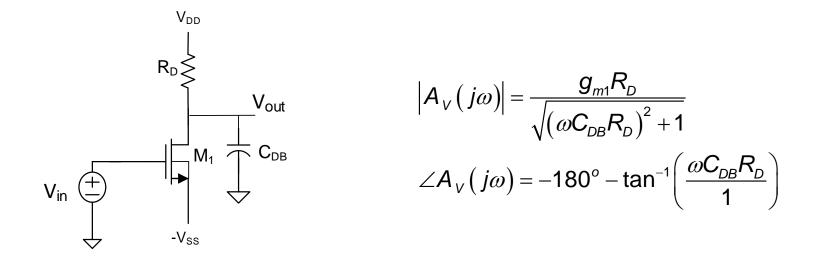

## **Amplifiers with Small Capacitors**

Consider parasitic  $C_{GS}$  and  $C_{DB}$

Solving:

$$\frac{v_{\rm OUT}}{v_{\rm IN}} = \frac{-g_{\rm m1}}{sC_{\rm DB}+G_{\rm D}}$$

Equivalently:

$$\frac{v_{\rm OUT}}{v_{\rm IN}} = \frac{-g_{m1}R_{\rm D}}{sC_{\rm DB}R_{\rm D}+1}$$

Response to Student Question from Last Lecture:

### $f_{\mathsf{T}}$ and $f_{\mathsf{MAX}}$ for a semiconductor process

$f_{\mathsf{T}}$  is defined to be the frequency where the short-circuit current gain of a transistor drops to unity

$f_{MAX}$  is defined to be the frequency where the power gain of the transistor drops to unity (related to the maximum frequency of oscillation in a process)

$$f_{T} \simeq \frac{3}{4\pi} \frac{\mu V_{EB}}{L_{\min}^{2}} = \frac{3}{16\pi} \frac{\mu \left| V_{DD} - V_{TH} \right|}{\left(\lambda - LD\right)^{2}}$$

$\rm f_{T}$  strongly dependent on  $\rm V_{EB}$

for the ON 0.5u process

$$u_n C_{OX} = 100 u A/V^2$$

$C_{OX} = 2.4 f F/u^2$

$\lambda = 0.2 u$

$LD = .05 u$

$V_{THn} = 0.8 V$

$u_n = 400 cm^2 A F^{-1} V^{-2}$

$At V_{EB} = 1V, f_T = 25 G Hz$

Note: As feature sizes shrink with process nodes,  $V_{EB-MAX}$  will typically drop linearly but  $L_{min}$  will drop quadratically thus  $f_T$  gets much larger in small feature processes

Response to Student Question from Last Lecture:

### $f_T$ and $f_{MAX}$ for a semiconductor process

Fig. 7. (a) Maximum stable gain (MSG) and maximum available gain (MAG) for different channel lengths and (b) the cutoff frequency  $(f_T)$  and maximum oscillation frequency  $(f_{max})$  as functions of the channel length.

For 0.18u process,  $V_D=2V$ ,  $V_G=1.2V$

Journal of the Korean Physical Society, Vol. 40, No. 1, January 2002, pp. 45~48

## **Amplifiers with Small Capacitors**

Consider parasitic  $C_{GS}$  and  $C_{DB}$

Sinusoidal Steady State Response for Linear Systems

$$V_{IN}(t) \longrightarrow A_v(s) \longrightarrow V_{OUT}(t)$$

#### Key Result from EE 201

If  $V_{IN} = V_m sin(\omega t + \theta)$  where  $V_m$  is small (so linear operation maintained)

Steady state output is also a sinusoid given by

$$V_{OUT}(t) = V_m |A_v(j\omega)| \sin(\omega t + \theta + \angle A_v(j\omega))$$

### Sinusoidal Steady State Response for Linear Systems

If  $V_{IN} = V_m \sin(\omega t + \theta)$

For V<sub>m</sub> small, small-signal steady state output given by

$$V_{OUT}(t) = V_m \frac{g_{m1}R_D}{\sqrt{\left(\omega C_{DB}R_D\right)^2 + 1}} \sin\left(\omega t + \theta - 180^\circ - \tan^{-1}\left(\frac{\omega C_{DB}R_D}{1}\right)\right)$$

# **Digital Circuit Design**

Most of the remainder of the course will be devoted to digital circuit design

# Verilog

module gates (input logic [3:0] a,b, output logic [3:0] y1,y2,y3,y4,y5); assign y1 = a&b; //AND assign y2 = a | b; //OR assign y3 = a ^ b; //XOR assign y4 = ~(a & b); //NAND assign y5 = ~(a | b); //NOR endmodule

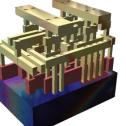

A rendering of a small standard cell with three metal layers (<u>dielectric</u> has been removed). The sand-colored structures are metal interconnect, with the vertical pillars being contacts, typically plugs of tungsten. The reddish structures are <u>polysilicon</u> gates, and the solid at the bottom is the crystalline silicon bulk

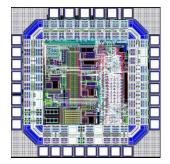

#### Standard Cell Library

#### VHDL

library IEEE; use IEEE.STD\_LOGIC\_1164.all;

entity gates is

port(a,b: in STD\_LOGIC\_VECTOR(3 dowto 0); y1,y2,y3,y4,y5:out STD\_LOGIC\_VECTOR(3 downto 0)); end;

3.5V

Α –

c –

В

architecture synth of gates is begin

y1 <= a and b; y2 <= a or b; y3 <= a xor b; y4 <= a nand b; y5 <= a nor b; end;

# **Digital Circuit Design**

**Hierarchical Design**

- Basic Logic Gates

- Properties of Logic Families

- Characterization of CMOS

Inverter

- Static CMOS Logic Gates

- Ratio Logic

- Propagation Delay

- Simple analytical models

- FI/OD

- Logical Effort

- Elmore Delay

- Sizing of Gates

- The Reference Inverter

- Propagation Delay with Multiple Levels of Logic

- Optimal driving of Large Capacitive Loads

- Power Dissipation in Logic Circuits

- Other Logic Styles

- Array Logic

- Ring Oscillators

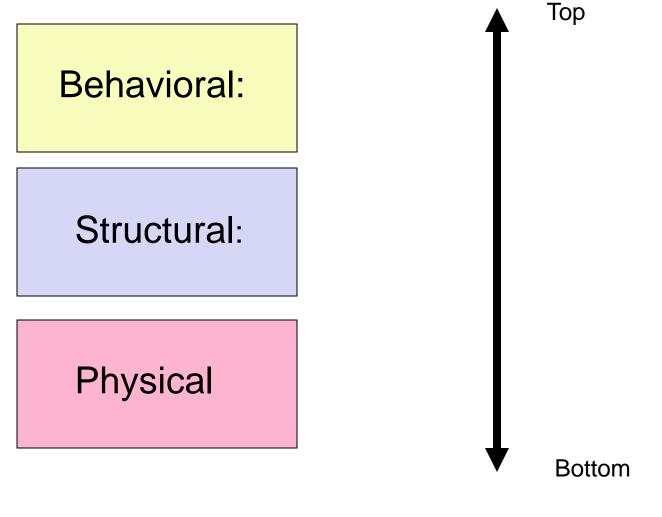

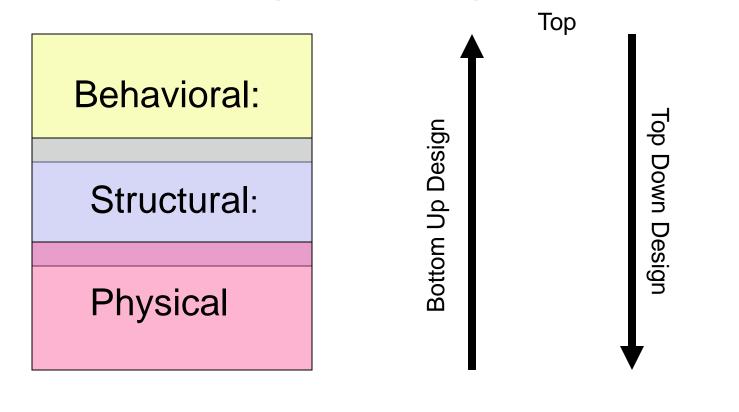

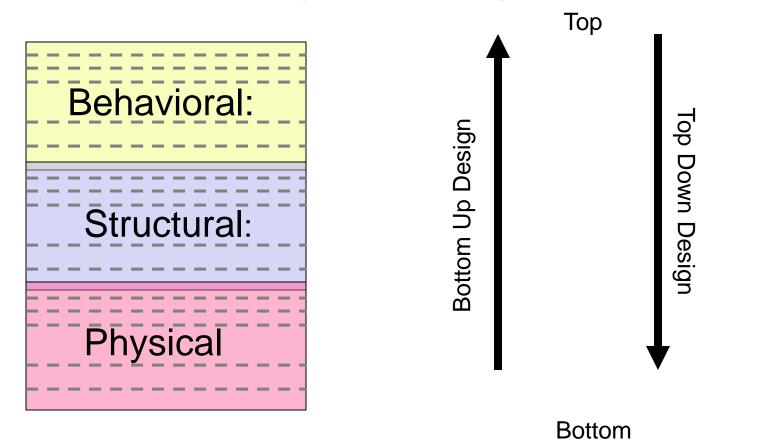

**Multiple Levels of Abstraction**

**Bottom**

Multiple Sublevels in Each Major Level All Design Steps may not Fit Naturally in this Description

Behavioral: Describes what a system does or what it should do

- **Structural :** Identifies constituent blocks and describes how these blocks are interconnected and how they interact

- **Physical :** Describes the constituent blocks to both the transistor and polygon level and their physical placement and interconnection

Multiple representations often exist at any level or sublevel

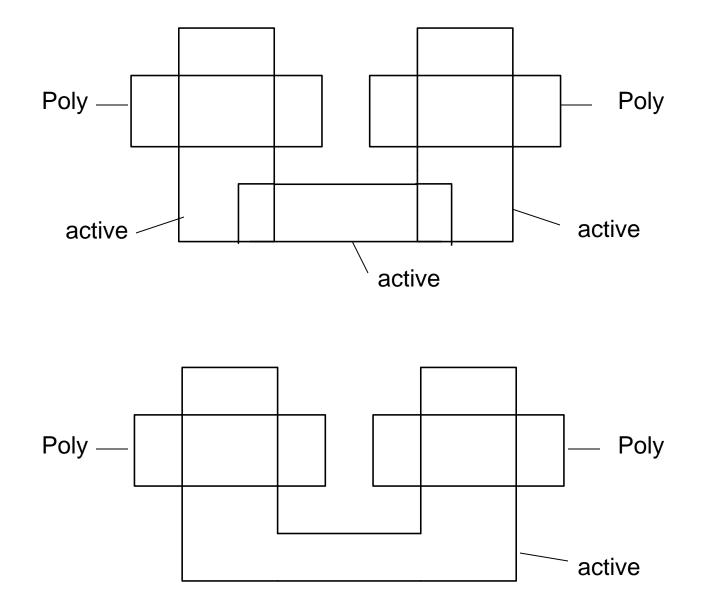

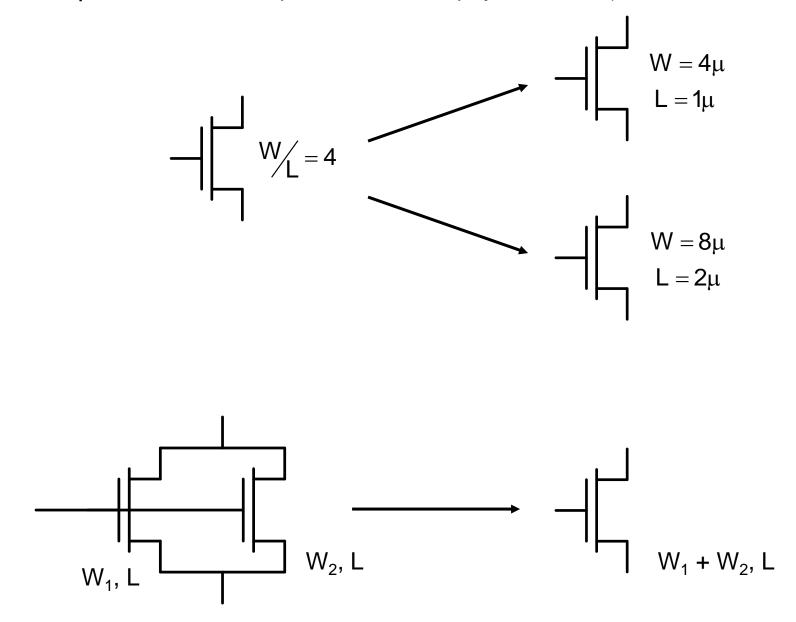

Example: Two distinct representations at the physical level (polygon sublevel)

Example: Two distinct representations at physical level (schematic sublevel)

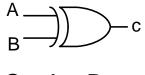

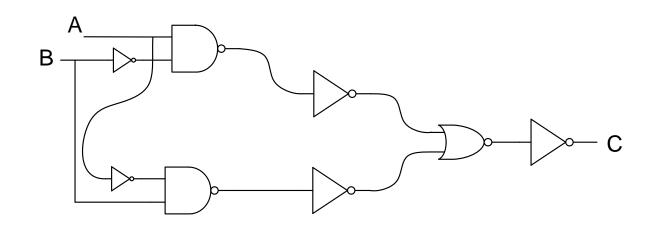

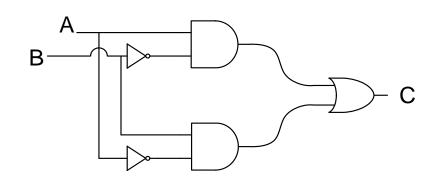

Example: Three distinct representations at the structural/behavioral level (gate sublevel)

$C = A \oplus B$

In each domain, multiple levels of abstraction are generally used.

#### Consider Physical Domain

- Consider lowest level to highest

- 0 placement of diffusions, thin oxide regions, field oxide, ect. on a substrate.

- polygons identify all mask information (not unique)

- 2 transistors (not unique)

- 3 gate level (not unique)

- 4 cell level

Adders, Flip Flop, MUTs,...

#### **Information Type**

PG data G.D.F Netlist HDL Description

#### Structural Domain:

- DSP

- Blocks (Adders, Memory, Registers, etc.

- Gates

- Transistor

**Information Type**

HDL

**Netlists**

#### Behavior Domain (top down):

- Application

- Programs

- Subroutines

- Boolean Expressions

#### Information Type

High-Level Language HDL

### **Representation of Digital Systems**

### Standard Approach to Digital Circuit Design

#### 8 – level representation

- 1. Behavioral Description

- Technology independent

- 2. RTL Description (Register Transfer Level)

(must verify (1)  $\Leftrightarrow$  (2))

3. RTL Compiler

**Registers and Combinational Logic Functions**

- 4. Logic Optimizer

- 5. Logic Synthesis

Generally use a standard call library for synthesis

(sublevels 6-8 not shown on this slide)

## Frontend design

**Representation of Digital Systems**

Standard Approach to Digital Circuit Design

- 1. Behavioral Description

- Technology independent

- 2. RTL Description

- (must verify (1)  $\Leftrightarrow$  (2))

- 3. RTL Compiler

**Registers and Combinational Logic Functions**

4. Logic Optimizer

### 5. Logic Synthesis

Generally use a standard call library for synthesis

## **Backend design**

### 6. Place and Route

(physically locates all gates and registers and interconnects them)

- 7. Layout Extraction

- DRC

- Back Annotation

- 8. Post Layout simulation

May necessitate a return to a higher level in the design flow

Logic synthesis, though extensively used, often is not as efficient nor as optimal for implementing some important blocks or some important functions

These applications generally involve transistor level logic circuit design that may combine one or more different logic design styles

# Logic Optimization

What is optimized (or minimized) ?

- Number of Gates

- Number or Levels of Logic

- Speed

- Delay

- Power Dissipation

- Area

- Cost

- Peak Current

- • •

Depends Upon What User Is Interested In

# Standard Cell Library

- Set of primitive building blocks that have been pre-characterized for dc and high frequency performance

- Generally includes basic multiple-input gates and flip flops

- P-cells often included

- Can include higher-level blocks

- Adders, multipliers, shift registers, counters,...

- Cell library often augmented by specific needs of a group or customer

# **Digital Circuit Design**

- Hierarchical Design

- **Basic Logic Gates**

- Properties of Logic Families

- Characterization of CMOS Inverter

- Static CMOS Logic Gates

- Ratio Logic

- Propagation Delay

- Simple analytical models

- FI/OD

- Logical Effort

- Elmore Delay

- Sizing of Gates

- The Reference Inverter

- Propagation Delay with Multiple Levels of Logic

- Optimal driving of Large Capacitive Loads

- Power Dissipation in Logic Circuits

- Other Logic Styles

- Array Logic

- Ring Oscillators

# Logic Circuit Block Design

### Many different logic design styles

•Static Logic Gates

•Complex Logic Gates

Pseudo NMOS

•Pass Transistor Logic

•Dynamic Logic Gates

•Domino Logic

•Zipper Logic

•Output Prediction Logic

Various logic design styles often combined in the implementation of one logic block

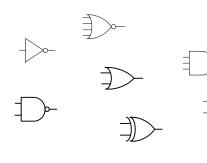

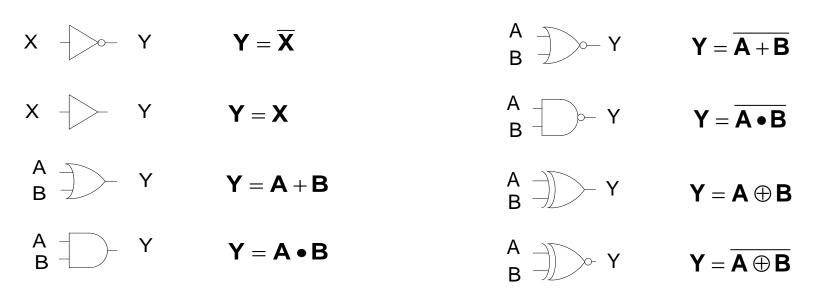

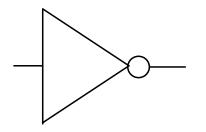

- $X \bigvee Y = \overline{X}$

- $X Y = \mathbf{X}$

- $\begin{array}{c} A \\ B \end{array} \longrightarrow \begin{array}{c} Y \\ \end{array} Y = \mathbf{A} + \mathbf{B}$

- $\begin{array}{c} \mathsf{A} \\ \mathsf{B} \end{array} \begin{array}{c} & \mathsf{Y} \end{array} \qquad \qquad \mathsf{Y} = \mathsf{A} \bullet \mathsf{B} \end{array}$

- $\begin{array}{c} \mathsf{A} \\ \mathsf{B} \end{array} \begin{array}{c} & & \\ \end{array} \begin{array}{c} \mathsf{P} \\ \mathsf{P} \end{array} \end{array} \begin{array}{c} \mathsf{P} \\ \mathsf{P} \end{array} \begin{array}{c} \mathsf{P} \\ \mathsf{P} \end{array} \end{array} \begin{array}{c} \mathsf{P} \\ \mathsf{P} \end{array} \begin{array}{c} \mathsf{P} \\ \mathsf{P} \end{array} \end{array}$

- $\begin{array}{c} \mathsf{A} \\ \mathsf{B} \end{array} \begin{array}{c} \frown \\ \mathsf{P} \end{array} \begin{array}{c} \mathsf{Y} \end{array} \qquad \mathbf{Y} = \overline{\mathbf{A} \bullet \mathbf{B}}$

- $\begin{array}{c} \mathsf{A} \\ \mathsf{B} \end{array} \begin{array}{c} \longrightarrow \mathsf{Y} \end{array} \qquad \qquad \mathsf{Y} = \mathsf{A} \oplus \mathsf{B} \end{array}$

- $\begin{array}{c} \mathsf{A} \\ \mathsf{B} \end{array} ) \begin{array}{c} & & \\ \end{array} \mathbf{Y} \\ \mathbf{Y} \end{array} = \overline{\mathbf{A} \oplus \mathbf{B}}$

- $A \rightarrow AOI$ B  $C \rightarrow P$ D  $Y = \overline{A \cdot B + C \cdot D}$

>>- Y

— Y

$A_1$

$A_1$

$A_1$

$A_1$  $A_n$

- $\mathbf{Y} = \overline{\left(\mathbf{A} + \mathbf{B}\right) \bullet \left(\mathbf{C} + \mathbf{D}\right)}$

- $\mathbf{Y} = \mathbf{A}_1 + \mathbf{A}_2 + \dots \mathbf{A}_n$

- $\mathbf{Y} = \overline{\mathbf{A}_1 + \mathbf{A}_2 + \dots \mathbf{A}_n}$

- $\mathbf{Y} = \mathbf{A}_1 \bullet \mathbf{A}_2 \bullet \dots \mathbf{A}_n$

- $\mathbf{Y} = \overline{\mathbf{A}_1 \bullet \mathbf{A}_2 \bullet ... \mathbf{A}_n}$

Question: How many basic one and two input gates exist and how many of these are useful?

### The set of NOR gates is complete

Any combinational logic function can be realized with only multiple-input NOR gates

### The set of NAND gates is complete

Any combinational logic function can be realized with only multiple-input NAND gates

Performance of the BASIC gates is critical!

A gate logic family can be formed based upon a specific design style for implementing logic functions

Many different gate logic family types exist NMOS, PMOS, CMOS, TTL, ECL, RTL, DCTL,... Substantial differences in performance from one family type to another

Power, Area, Noise Margins, ....

# The basic logic gates

It suffices to characterize the inverter of a logic family and then express the performance of other gates in that family in terms of the performance of the inverter.

What characteristics are required and desirable for an inverter to form the basis for a useful logic family?

What restrictions are there on the designer for building Boolean circuits?

• None !!!!

• It must "work" as expected

• Designer is Master of the silicon !

What are the desired characteristics of a logic family?

- 1. High and low logic levels must be uniquely distinguishable (even in a long cascade)

- 2. Capable of driving many loads (good fanout)

- 3. Fast transition times (but in some cases, not too fast)

- 4. Good noise margins (low error probabilities)

- 5. Small die area

- 6. Low power consumption

- 7. Economical process requirements

- 8. Minimal noise injection to substrate

- 9. Low leakage currents

- 10. No oscillations during transitions

- 11. Compatible with synthesis tools

- 12. Characteristics do not degrade too much with temperature

- 13. Characteristics do not vary too much with process variations

Are some of these more important than others?

- 8. Minimal noise injection to substrate

- 9. Low leakage currents

- 10. No oscillations during transitions

- 11. Compatible with synthesis tools

- 12. Characteristics do not degrade too much with temperature

- 13. Characteristics do not vary too much with process variations

Are some of these more important than others?

Yes ! – must have well-defined logic levels for circuits to even function as logic

Are some of these more important than others?

Yes ! – must have well-defined logic levels for circuits to even function as logic

What properties of an inverter are necessary for it to be useful for building a logic family

What are the logic levels for a given inverter of for a given logic family?

#### Can we legislate them ?

- Some authors choose to simply define a value for them

- Simple and straightforward approach

- But what if the circuit does not interpret them the same way they are defined !!

#### Can we legislate them ?

In 1897 the Indiana House of

Representatives unanimously passed a measure redefining the area of a circle and the value of pi. (House Bill no. 246, introduced by Rep. Taylor I. Record.) The bill died in the state Senate.

#### WIKIPEDIA The Free Encyclopedia

Main page Contents Current events Random article About Wikipedia Contact us Donate

Contribute

Help Learn to edit

### Indiana Pi Bill

From Wikipedia, the free encyclopedia

The **Indiana Pi Bill** is the popular name for bill #246 of the 1897 sitting of the Indiana General Assembly, one of the most notorious attempts to establish mathematical truth by legislative fiat. Despite its name, the main result claimed by the bill is a method to square the circle, although it does imply various incorrect values of the mathematical constant  $\pi$ , the ratio of the circumference of a circle to its diameter.<sup>[1]</sup> The bill, written by a physician who was an amateur mathematician, never became law due to the

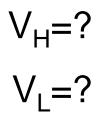

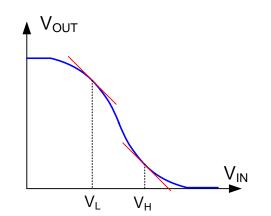

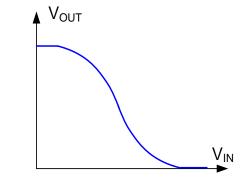

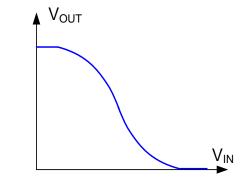

**Noise Margins** The static operation of a logic-circuit family is characterized by the voltage transfer characteristic (VTC) of its basic inverter. Figure 10.2 shows such a VTC and defines its four parameters;  $V_{OH}$ ,  $V_{OL}$ ,  $V_{IH}$ , and  $V_{IL}$ . Note that  $V_{IL}$  and  $V_{IL}$  are defined as the points at which the slope of the VTC is -1. Also indicated is the definition of the threshold voltage  $V_{M}$ , or  $V_{th}$  as we shall frequently call it, as the point at which  $v_{O} = v_{I}$ . Recall that we discussed the VTC in its generic form in Section 1.7, and have also seen actual VTCs in Section 4.10 for the CMOS inverter, and in Section 5.10 for the BJT inverter.

The **robustness** of a logic-circuit family is determined by its ability to reject noise, and thus by the noise margins  $NH_H$  and  $NM_L$ ,

$$NM_H \equiv V_{OH} - V_{IH} \tag{10.1}$$

$$NM_L \equiv V_{IL} - V_{OL}$$

FIGURE 10.2 Typical voltage transfer characteristic (VTC) of a logic inverter, illustrating the definition of the critical points.

#### Can we legislate them ?

World's most widely used electronics text

Can we legislate them ?

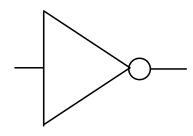

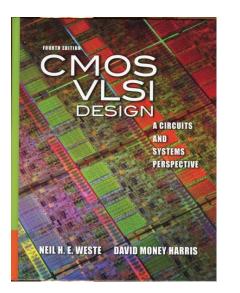

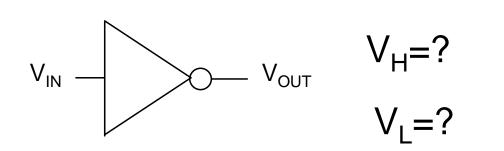

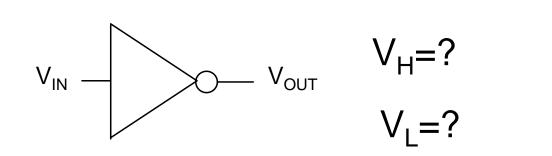

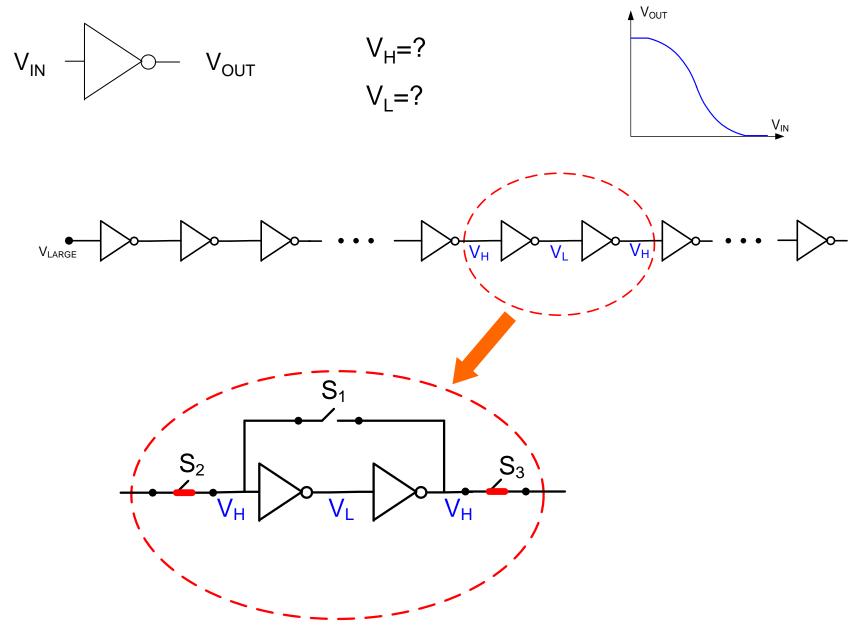

$V_{H}=?$   $V_{L}=?$

Can we legislate them ?

- Some authors choose to define them based upon specific features of inverter

- Analytical expressions may be complicated

- But what if the circuit does not interpret them the same way they are defined !!

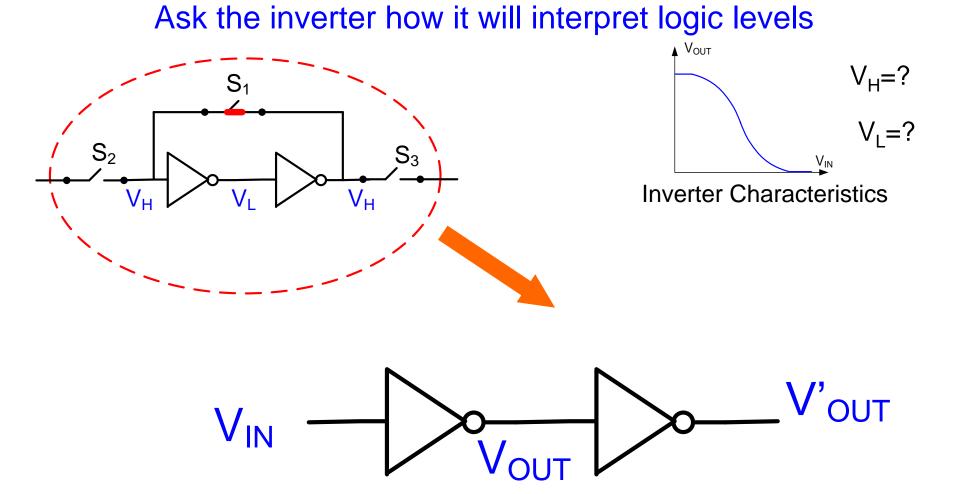

Ask the inverter how it will interpret logic levels

- The inverter <u>will</u> interpret them the way the circuit really operate as a Boolean system !!

- · Analytical expressions may be complicated

- · How is this determination made?

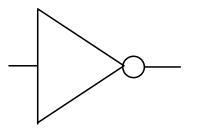

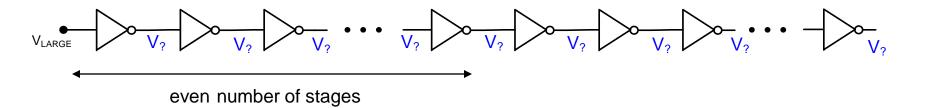

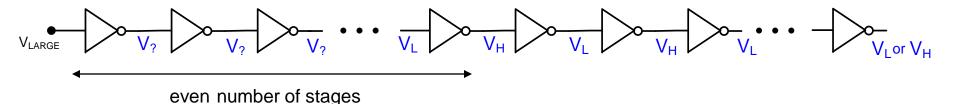

Consider a very long cascade of inverters

Apply a large voltage at the input (alternatively a small input could be used) w.l.o.g. assume an even number of inverters in chain indicated

Consider a very long cascade of inverters

Apply a large voltage at the input (alternatively a small input could be used) w.l.o.g. assume an even number of inverters in chain indicated

If logic levels are to be maintained, the voltage at the end of this even number of stages must be  $V_H$ , that of the next must be  $V_L$ , the next  $V_H$ , etc. until the start of the cascade is approached

### ↓ V<sub>OUT</sub> $V_{H}=?$ $S_1$ V<sub>L</sub>=? $S_2$ $S_3$ V<sub>IN</sub> V<sub>H</sub> V<sub>H</sub>

Ask the inverter how it will interpret logic levels

- Two inverter loop

- Very useful circuit !

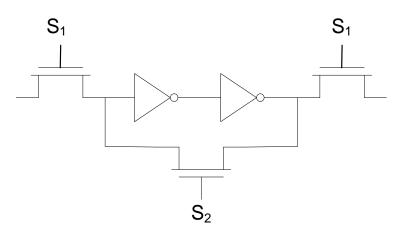

### The two-inverter loop

### The two-inverter loop

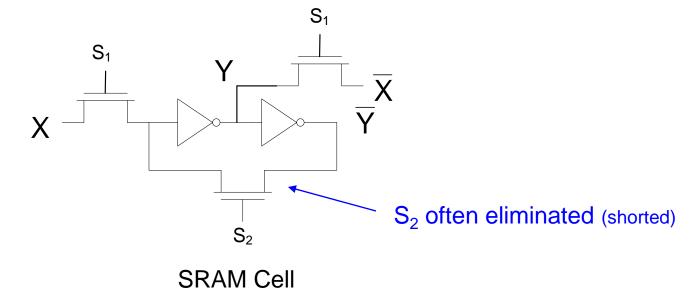

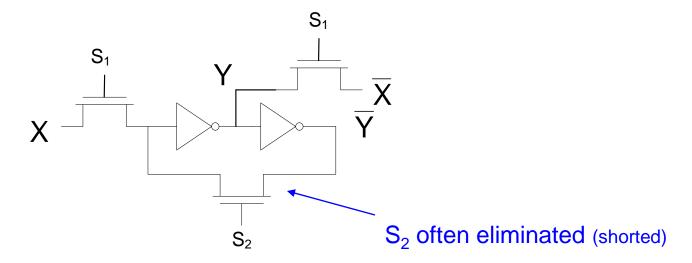

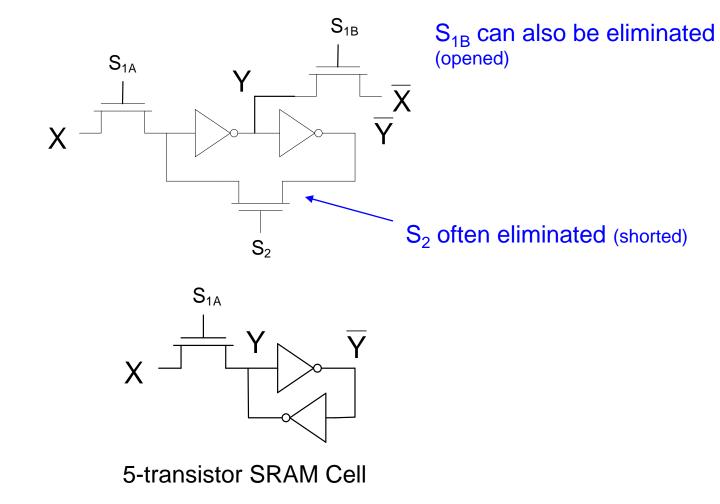

Standard 6-transistor SRAM Cell

## The two-inverter loop

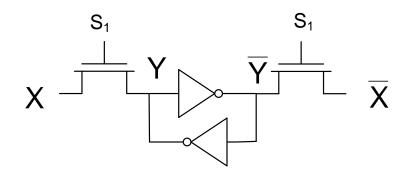

Will also work but less common (less area but degraded performance)

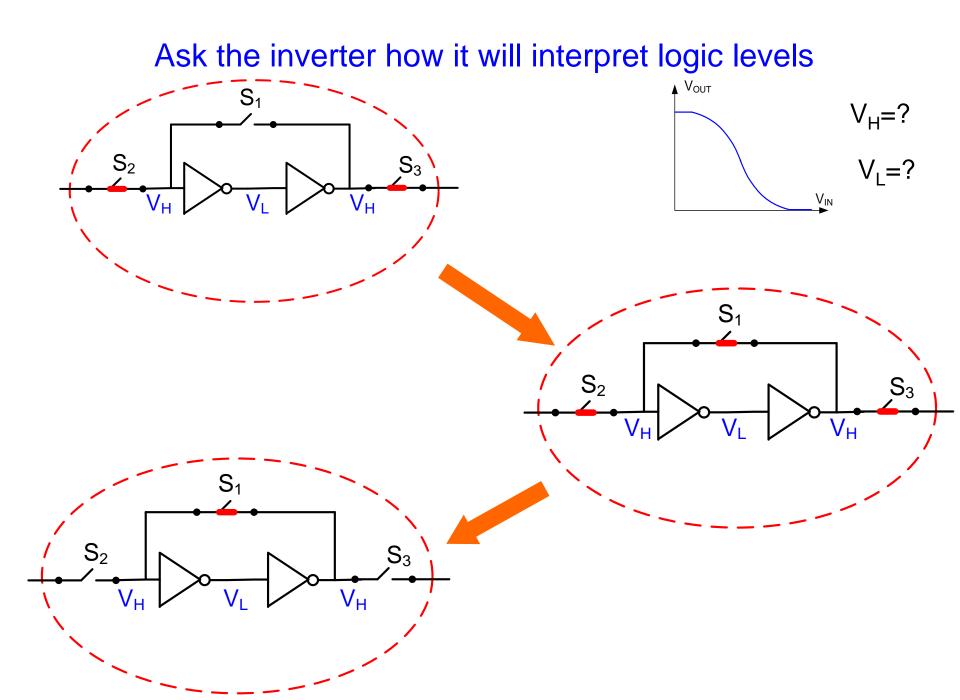

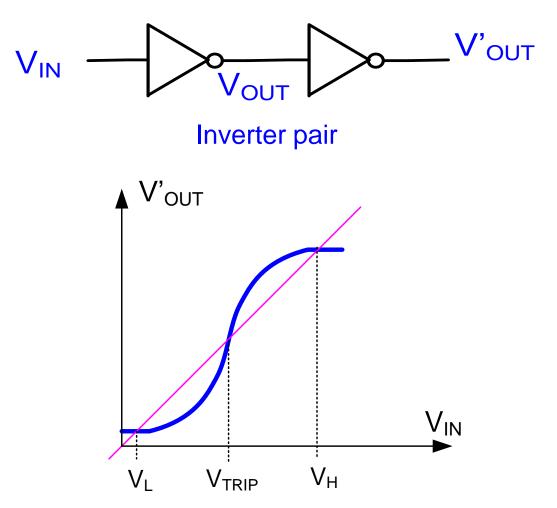

Thus, consider the inverter pair

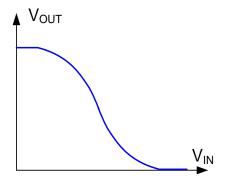

### Ask the inverter how it will interpret logic levels **↓** V<sub>OUT</sub> V'out $V_{H}=?$ $V_{\text{IN}}$ /<sub>OUT</sub> $V_1 = ?$ $V_{\text{IN}}$ **Inverter** pair $V_{H}$ and $V_{I}$ will be on the intersection of the transfer characteristics of the inverter pair (IPTC) and the $V'_{OUT}=V_{IN}$ line V'<sub>OUT</sub> V'<sub>OUT</sub>=V<sub>IN</sub> $V_{IN}$

$V_H$  and  $V_L$  often termed the "1" and "0" states

When  $V'_{OUT} = V_{IN}$ ,  $V_H$  and  $V_L$  are stable operating points,  $V_{TRIP}$  is a quasi-stable operating point

Observe: slope of IPTC is greater than 1 at  $V_{TRIP}$  and less than 1 at  $V_H$  and  $V_L$

# Stay Safe and Stay Healthy !

# End of Lecture 36

What Characteristics of a Logic Family are Desirable?

Student List:

- Speed • •

- (ility)